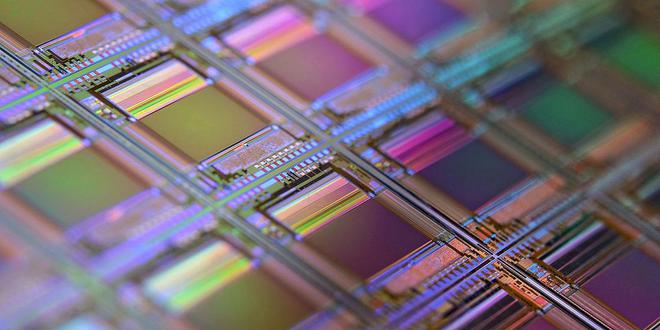

近日台积电(TSMC)举办了 2024 年北美技术论坛,揭示了其最新的制程技术、先进封装技术、以及三维立体电路(3D IC)技术,以驱动下一代人工智能(AI)的创新。其中台积电首次公布了 A16 制程工艺,将结合纳米片晶体管和背面供电解决方案,以提升逻辑密度和能效,预计 2026 年量产。

据相关媒体报道,台积电向参与会议的人士透露,A16 制程工艺不需要下一代 High-NA EUV 光刻系统参与。这意味着台积电已经找到了在现有 EUV 光刻系统重经济高效地使用双重曝光等方法,将临界尺寸提高到 13nm 以上。不过台积电并没有停止探索在未来制程工艺中使用 High-NA EUV 光刻技术的步伐,紧随 A16 之后的 A14 制程工艺就会引入新的光刻技术。

台积电在此前的报告中表示,目前开发中的 A14 制程工艺旨在进一步改善频率、功率、密度和成本的表现,项目进展良好。台积电将继续探索 High-NA EUV 光刻技术的使用,对薄膜掩膜板等进行研究,以支持前沿技术并扩展摩尔定律。

使用 High-NA EUV 光刻系统将大大增加晶圆厂的成本,根据配置的不同,设备的价格约在 3.85 亿美元起步。芯片制造商更倾向于重复利用现有的工具,所以台积电也尽可能地避免使用 High-NA EUV 光刻系统,除非原有的 EUV 光刻系统无法继续改进生产能力。与此同时,台积电也在相关光刻材料上下功夫,以提高光刻工艺和良品率。

台积电这次公布 A16 制程工艺多少有点让人感到意外,随着人工智能行业加速发展、需求攀升,台积电似乎加快了制程技术的开发。